Loading...

Loading...

General information

OSCAR — The programming system for Operative Synthesis of Computers from

Algorithmic Representation.

OSCAR — The programming system for Operative Synthesis of Computers from

Algorithmic Representation.

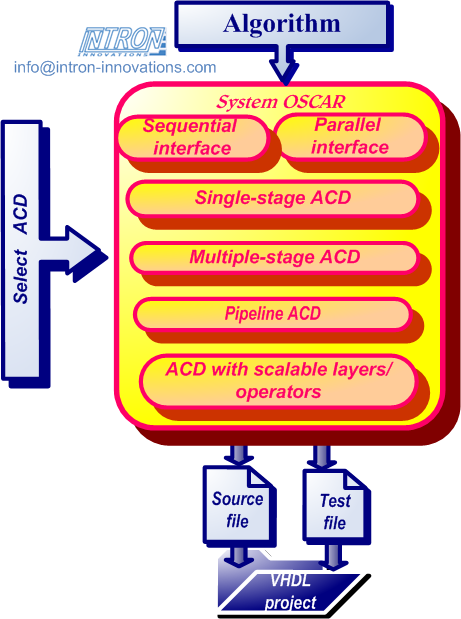

OSCAR is the programming system for operative synthesis of algorithmic computing devices (ACD)

intended for the automatic generation of an ASICs design from the algorithmic representation.

OSCAR allows synthesis of various options of ACD, from single clock to multiclock.

The developer, specifying an algorithm of the data processing on algorithmic representation,

gets on return fully debugged and synthesizable VHDL model of the device that implements

described algorithm.

The architecture of the device is fully optimized for the executed algorithm and maximally uses

its ability for paralleling. Obtained VHDL design may be further implemented in FPGA by any

available FPGA design solution.

OSCAR Features

• computer schematic synthesis without human's assistance;

• customer can select one of the following options for the synthesis of the ACD:

a) single-stage ACD;

b) multiple-stage ACD;

c) pipeline ACD;

d) ACD with scalable layers/operators;

• automatic generation of the test bench.

Data flow organization

• IEEE-754 data format;

• parallel interface;

• sequential interface.

Algorithmic computing device (ACD) types and features

• adaptable to external environment interface;

• ACD with scalable layers/operators;

• single-stage ACD;

• multiple-stage ACD;

• pipeline ACD.