Loading...

Loading...

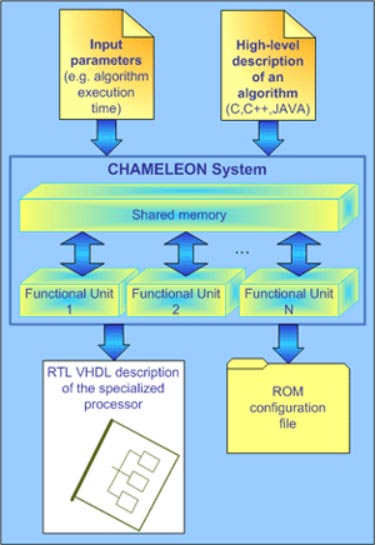

CHAMELEON – the System-Level Design Solution developed by INTRON – is intended for ASIC design automatic generation from the algorithm described on ANSI C language. The developer, specifying an algorithm of the data processing on ANSI C, gets on return fully debugged and synthesizable VHDL RTL model of the device that implements described algorithm. The architecture of the device is fully optimized for the executed algorithm and maximally uses its ability for paralleling. Obtained VHDL design may be further implemented in FPGA by any FPGA design solution, e.g. Xilinx ISE WebPACK. On current phase of development, the CHAMELEON is optimized for Xilinx Virtex FPGAs, and it is being optimized for Altera's FPGAs.

The CHAMELEON System involves both hardware and software parts.

One of the base elements of the hardware subsystem is a processor with the configurable architecture that turns into the specialized processors according to the specified input parameters thus implementing algorithm described on C language. The component parts of a processor are the Control Unit and a set of the Functional Modules with the shared memory. The application of an appropriate set of the Functional Units working in parallel gives an opportunity to get maximum performance for the specified algorithm.

An outcome of the software subsystem work is automatic determination of processor's specific parameters and generation of a ROM configuration program.